# Space product assurance

Qualification of printed circuit boards

Published by: ESA Publications Division

ESTEC, P.O. Box 299, 2200 AG Noordwijk, The Netherlands

ISSN: 1028-396X

Price: € 30

Printed in The Netherlands

Copyright 2001  $\ensuremath{^{\odot}}$  by the European Space Agency for the members of ECSS

# **Foreword**

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering and product assurance in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards.

Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

The formulation of this Standard takes into account the existing ISO 9000 family of documents.

This Standard has been prepared by the ECSS Q-70-10 Working Group, reviewed by the ECSS Technical Panel and approved by the ECSS Steering Board.

This Standard is based on ESA PSS-01-710, CNES/QFT/SP. 0117, CNES/QFT/SP. 0118, CNES/QFT/SP. 0119, CNES/QFT/SP. 0120 (draft).

(This page is intentionally left blank)

# Introduction

PCBs are used for the mounting of components in order to produce printed board assemblies performing complex electrical functions. The PCBs are subjected to thermal and mechanical shocks during their assembly such as mounting of components by soldering, rework and repair under normal terrestrial conditions, and in addition the complex printed board assembly are subjected to the environment imposed by launch and space flights.

(This page is intentionally left blank)

# **Contents**

| For  | eword                                    | 3  |

|------|------------------------------------------|----|

| Intr | oduction                                 | 5  |

| 1    | Scope                                    | 13 |

| 2    | Normative references                     | 15 |

| 3    | Terms, definitions and abbreviated terms | 17 |

| 3.1  | Terms and definitions                    | 17 |

| 3.2  | Abbreviated terms                        | 20 |

| 4    | General                                  | 21 |

| 5    | Evaluation                               | 23 |

| 5.1  | General                                  | 23 |

| 5.2  | Request for evaluation                   | 23 |

| 5.3  | Evaluation printed board samples         | 23 |

| 5.4  | Line audit                               | 24 |

| 6    | Qualification                                                                                    | 25 |

|------|--------------------------------------------------------------------------------------------------|----|

| 6.1  | General                                                                                          | 25 |

| 6.2  | Qualification sequence                                                                           | 25 |

| 6.3  | Qualification test programme                                                                     | 26 |

| 6.4  | Qualification test board                                                                         | 29 |

| 6.5  | Qualification programme                                                                          | 39 |

| 7    | Test and inspections                                                                             | 41 |

| 7.1  | Test condition                                                                                   | 41 |

| 7.2  | Test descriptions                                                                                | 41 |

| 8    | Group 1 — Initial test                                                                           | 43 |

| 8.1  | Subgroup 1.0 - Visual inspection and non-destructive test                                        | 43 |

| 8.2  | Subgroup 1.1 — Specific dimensional check                                                        | 48 |

| 8.3  | Subgroup 1.2 — Electrical measurements                                                           | 49 |

| 9    | Group 2 — Miscellaneous tests                                                                    | 51 |

| 9.1  | Subgroup 2.1 — Solderability test — Wettability on specimen J                                    | 51 |

| 9.2  | Subgroup 2.2 — Mechanical tests                                                                  | 52 |

| 9.3  | Subgroup 2.3 — Coatings tests                                                                    | 54 |

| 9.4  | Subgroup 2.4 — Electrical tests                                                                  | 60 |

| 9.5  | Subgroup 2.5 — Physical tests on specimen K                                                      | 62 |

| 10   | Group 3 — Thermal stress and thermal shock (on board)                                            | 63 |

| 10.  | General                                                                                          | 63 |

| 10.2 | Solder bath float method and vapour phase reflow simulation method (on board without specimen F) | 63 |

| 10.3 | Rework simulation (thermal shock, hand soldering) on specimen ${\sf F}\ldots\ldots$              | 64 |

| 11   | Group 4 — Thermal cycling (on board)                                                             | 65 |

| 12   | Group 5 — Damp heat — Steam ageing (on board)                                                    | 67 |

| 12.  | Damp heat on board without specimen F                                                            | 67 |

| 12.2 | Steam ageing on specimen F                                                                       | 68 |

| 13 Qu  | alification approval                                   | 69 |

|--------|--------------------------------------------------------|----|

| 13.1   | General customer qualification                         | 69 |

| 13.2   | Validation of qualification                            | 69 |

| 14 Mai | intenance of qualification                             | 71 |

| 14.1   | General                                                | 71 |

| 14.2   | Maintenance                                            | 71 |

| 14.3   | Qualification withdrawal                               | 72 |

| 15 Qu  | ality assurance for manufacturing                      | 73 |

| 15.1   | General                                                | 73 |

| 15.2   | Data                                                   | 73 |

| 15.3   | Nonconformance                                         | 73 |

| 15.4   | Incoming inspection of raw materials                   | 73 |

| 15.5   | Traceability                                           | 73 |

| 15.6   | Calibration                                            | 74 |

| 15.7   | Workmanship standards                                  | 74 |

| 15.8   | Inspection                                             | 74 |

| 15.9   | Operator and inspector training                        | 74 |

| 15.10  | Quality test specimen                                  | 74 |

| 15.11  | Microsection                                           | 74 |

| 15.12  | Final inspection and tests                             | 74 |

| 16 Qu  | ality assurance for delivery                           | 75 |

| 16.1   | Packaging                                              | 75 |

| 16.2   | Documentation                                          | 75 |

| 17 Min | imum requirements acceptable for high reliability PCBs | 77 |

| 17.1   | General                                                | 77 |

| 17.2   | Rigid single-sided and double-sided printed boards     | 78 |

| 17.3   | Flexible printed boards                                | 83 |

| 17.4   | Rigid-flex printed boards                              | 84 |

| 17.5   | Rigid multilayer printed boards                        | 85 |

| 17.6   | Sequential rigid multilaver printed boards             | 88 |

| Annex A    | (informative) Index of test descriptions                                                                           | 91  |

|------------|--------------------------------------------------------------------------------------------------------------------|-----|

| Annex B    | (informative) Example of evaluation test report                                                                    | 93  |

| Annex C    | (informative) Example of check-list                                                                                | 95  |

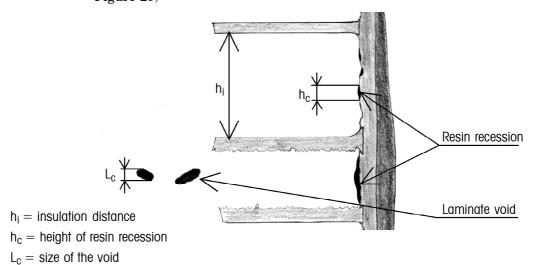

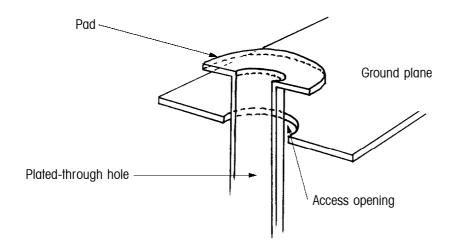

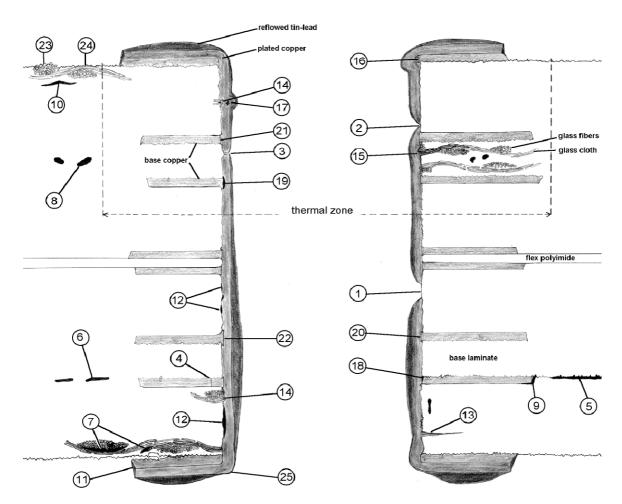

| Annex D    | (informative) Example of plated-through hole microsection                                                          | 101 |

| Bibliogra  | phy                                                                                                                | 103 |

| Figures    |                                                                                                                    |     |

| Figure 1:  | Qualification test flow chart                                                                                      | 26  |

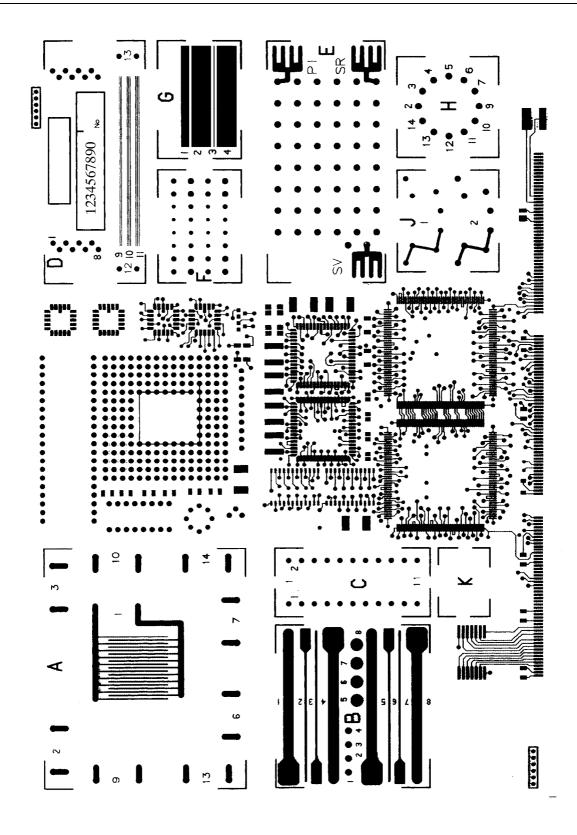

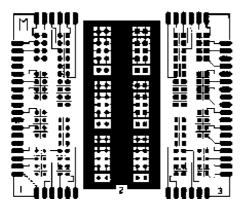

| Figure 2:  | Example of a qualification test board layout with test specimens and capability specimen                           | 31  |

| Figure 3:  | Example of test specimen layout for intralayer insulation resistance and dielectric withstanding voltage testing   | 32  |

| Figure 4:  | Example of test specimen layout for testing peel strength of conductors and pull-off strength of pads              | 33  |

| Figure 5:  | Example of test specimen layout for internal short circuit testing                                                 | 33  |

| Figure 6:  | Example of test specimen layout for etching definition evaluation and continuity testing                           | 34  |

| Figure 7:  | Example of test specimen layout for interconnection resistance and current overload testing                        | 34  |

| Figure 8:  | Example of test specimen layout for microsectioning and metal plating evaluation                                   | 35  |

| Figure 9:  | Example of test specimen layout for plating adhesion testing and analysis of SnPb coating composition after reflow | 35  |

| Figure 10: | Example of test specimen layout for interlayer insulation resistance and dielectric withstanding voltage testing   | 36  |

| Figure 11: | Example of test specimen layout for solder wettability and rework simulation testing                               | 36  |

| Figure 12: | Example of test specimen layout for water absorption and outgassing testing                                        | 37  |

| Figure 13: | Example of test specimen layout for evaluation of capability limits                                                | 37  |

| Figure 14: | Example of test specimen layout for evaluation of CAD/CAM capability                                               | 38  |

| Figure 15: | Example of test specimen layout for testing resistance to bending cycles                                           | 38  |

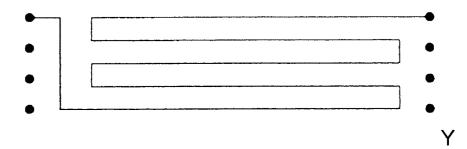

| Figure 16: | Example of test specimen layout for controlled impedance testing                                                   | 39  |

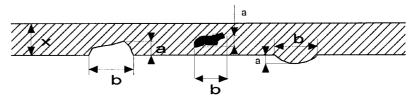

| Figure 17: | Random defects of conductors and terminal pads                                                                     | 45  |

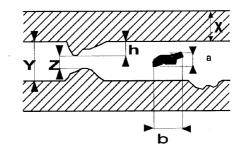

| Figure 18: | Random defects between two conductors                                                                              | 45  |

| Figure 10. | Misalianment of coverlay                                                                                           | 46  |

| Figure 20 | ): Warp                                                                                                                      | 47  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-----|--|

| Figure 21 | : Twist                                                                                                                      | 47  |  |

| Figure 22 | 2: Wettability of terminal pads and plated-through holes                                                                     | 52  |  |

| Figure 23 | 3: Dimensional parameters to be measured                                                                                     | 55  |  |

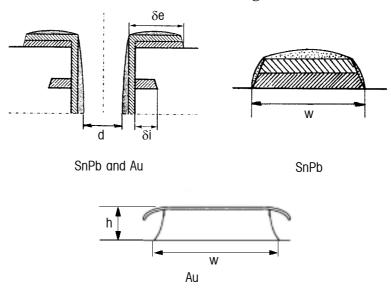

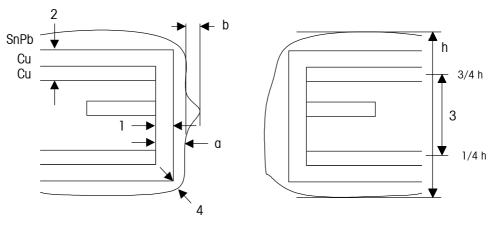

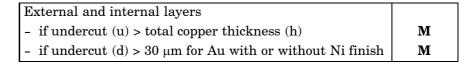

| Figure 24 | 4: Microsection of a PTH                                                                                                     | 56  |  |

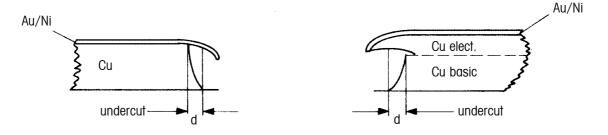

| Figure 25 | 5: Undercut for PCBs with fused SnPb finish                                                                                  | 57  |  |

| Figure 26 | 5: Undercut for PCBs with Au/Ni or Au finish                                                                                 | 57  |  |

| Figure 27 | 7: Overhang for PCBs with Au/Ni or Au finish                                                                                 | 58  |  |

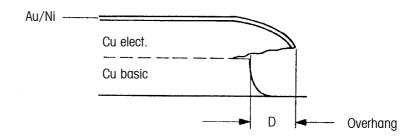

| Figure 28 | 3: Microsection in PTH: Possible defects                                                                                     | 59  |  |

| Figure 29 | P: Microsection of PTH: Possible defect                                                                                      | 59  |  |

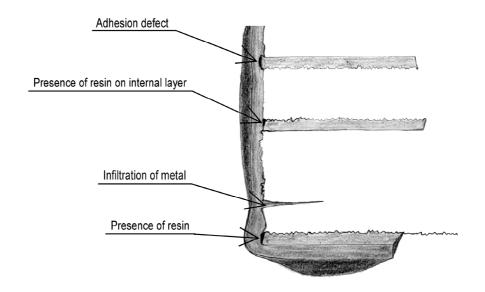

| Figure 30 | ): Voids in resin inside buried vias                                                                                         | 60  |  |

| Figure 3  | : Test for internal short circuit                                                                                            | 61  |  |

| Figure 32 | 2: Example of plated-through hole microsection                                                                               | 102 |  |

| Tables    |                                                                                                                              |     |  |

| Table 1:  | Test programme                                                                                                               | 27  |  |

| Table 2:  | Limits of approval and characteristics of finished rigid single-sided and double-sided boards                                | 78  |  |

| Table 3:  | Limits of approval and characteristics of finished rigid single-sided and double-sided boards for high frequency application | 80  |  |

| Table 4:  | Limits of approval and characteristics of finished flexible printed boards                                                   | 83  |  |

| Table 5:  | Limits of approval and characteristics of finished rigid multilayer printed boards                                           | 85  |  |

| Table 6:  | Limits of approval and characteristics of finished sequential rigid multilayer                                               | 88  |  |

(This page is intentionally left blank)

1

# Scope

This Standard defines the basic requirements for evaluation, qualification and maintenance of qualification of space PCB suppliers for different types of printed circuit boards.

This Standard is applicable to the following type of boards:

- rigid printed boards (single-sided, double-sided, multilayer, sequential-laminated multilayer and metal core);

- flexible printed boards (single-sided and double-sided);

- rigid-flex printed boards (multilayer and sequential-laminated multilayer);

- high frequency printed boards;

- special printed boards.

(This page is intentionally left blank)

# Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revisions of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated below. For undated references the latest edition of the publication referred to applies.

| ECSS-P-001                    | Glossary of terms                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECSS-Q-20                     | ${\bf Space\ product\ assurance-Quality\ assurance}$                                                                                                           |

| ECSS-Q-20-09                  | $\label{eq:space_product} Space\ product\ assurance\\ Nonconformance\ control\ system$                                                                         |

| ECSS-Q-70                     | Space product assurance — Material, mechanical parts and processes                                                                                             |

| ECSS-Q-70-02                  | Space product assurance — Thermal vacuum outgassing test for the screening of space materials                                                                  |

| ECSS-Q-70-08                  | Space product assurance — The manual soldering of high-reliability electrical connections                                                                      |

| ECSS-Q-70-11                  | $\label{eq:space_product} Space \ product \ assurance — Procurement \ of printed circuit boards$                                                               |

| ECSS-Q-70-21                  | $\begin{array}{ll} Space & product & assurance Flammability \\ testing for the screening of space materials \end{array}$                                       |

| ECSS-Q-70-22                  | Space product assurance — The control of limited shelf-life materials $$                                                                                       |

| ECSS-Q-70-29                  | Space product assurance — The determination of offgassing products from materials and assembled articles to be used in a manned space vehicle crew compartment |

| IEC 60068-2-3 (1969-01)       | Environmental testing. Part 2: Tests. Test Ca: Damp heat, steady state                                                                                         |

| IEC 60068-2-14-am 1 (1986-01) | Environmental testing. Part 2: Tests. Test $N$ :                                                                                                               |

Change of temperature

| IEC 60068-2-20-am 2 (1987-01) | Environmental testing. Part 2: Tests. Test T: Soldering                                                            |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| IEC 60249-1-am 4 (1993-05)    | Base materials for printed circuits. Part 1: Test methods                                                          |

| IEC 60326-2-am 1 (1992-06)    | Printed boards. Part 2: Test methods                                                                               |

| IEC 60326-5-am 1 (1989-10)    | Printed boards. Part 5: Specification for single and double sided printed boards with plated-through holes         |

| IEC 60326-8 (1981-01)         | Printed boards. Part 8: Specification for single and double sided flexible printed boards with through connections |

| IEC 60326-11 (1991-03)        | Printed boards. Part 11: Specification for flex-<br>rigid multilayer printed boards with through<br>connections    |

| IEC 62326-4 (1996-12)         | Printed boards. Part 4: Rigid multilayer printed boards with interlayer connnections – Sectional specification     |

| IPC-4101                      | Specification for base materials for rigid and multilayer printed boards                                           |

| MIL-P-50884C                  | Printed wiring, flexible and rigid-flex                                                                            |

3

# Terms, definitions and abbreviated terms

# 3.1 Terms and definitions

The following terms and definitions are specific to this Standard in the sense that they are complementary or additional to those contained in ECSS-P-001.

#### 3.1.1

#### blister

delamination in the form of a localized swelling and separation between any of the layers of a lamination base material, or between base material and conductive foil or protective coating

[IEC 60194 (1999-04)]

#### 3.1.2

# cover lay (flexible circuit)

the layer of insulating material that is applied covering totally or partially over a conductive pattern on the outer surfaces of a printed board

[IEC 60194 (1999-04)]

#### 3.1.3

## crazing

an internal condition that occurs in reinforced base material whereby glass fibres are separated from the resin at the weave intersections

NOTE 1 This condition manifests itself in the form of connected white spots or crosses that are below the surface of the base material. It is usually related to mechanically induced stress.

NOTE 2 See also "measling".

[IEC 60194 (1999-04)]

#### 3.1.4

#### delamination

a separation between plies within a base material, between base material and a conductive foil, or any other planar separation with a printed board (see also "Blister")

[IEC 60194 (1999-04)]

#### 3.1.5

#### dewetting

a condition that results when molten solder coats a surface and then recedes to leave irregularly-shaped mounds of solder that are separated by areas that are covered with a thin film of solder and with the basis metal not exposed

[IEC 60194 (1999-04)]

#### 3.1.6

#### flexible printed board

a printed board either single, double sided or multilayer consisting of a printed circuit or printed wiring using flexible base materials only [IEV 541-04-03, modified]

[IEC 60194 (1999-04)]

#### 3.1.7

#### haloing

mechanically-induced fracturing or delamination, on or below the surface of a base material, that is usually exhibited by a light area around holes or other machined features

[IEC 60194 (1999-04)]

#### 3.1.8

#### high frequency printed board

printed board used for high frequency applications, that has specific requirements for the dielectric properties of the base laminates as well as special dimensional requirements for the lay-out for electrical purposes

#### 3.1.9

#### inclusions

foreign particles, metallic or non-metallic, that may be entrapped in an insulating material, conductive layer, plating, base material or solder connection

[IEC 60194 (1999-04)]

#### 3.1.10

# key personnel

personnel with specialist knowledge responsible for defined production or product assurance areas

#### 3.1.11

#### measling

a condition that occurs in laminated base material in which internal glass fibres are separated from the resin at the weave intersection

NOTE 1 This condition manifests itself in the form of discrete white spots or "crosses" that are below the surface of the base material. It is usually related to thermally-induced stress.

NOTE 2 See also "crazing"

[IEC 60194 (1999-04)]

#### 3.1.12

## metal core printed board

printed board using a metal core base material [IEV 541-04-03] [IEC 60194 (1999-04)]

#### 3.1.13

#### multilayer printed board

the general term for a printed board that consist of rigid or flexible insulation materials and three or more alternate printed wiring and/or printed circuit layers that have been bonded together and electrically interconnected

[IEC 60194 (1999-04)]

#### 3.1.14

#### prepreg

a sheet of material that has been impregnated with a resin and cured to an intermediate stage, i.e. B-staged resin

[IEC 60194 (1999-04)]

#### 3.1.15

#### printed board

the general term for completely processed printed circuit and printed wiring configurations

NOTE This includes single-sided, double sided and multilayer boards with rigid, flexible, and rigid-flex base materials. [IEV 541-04-03, modified]

[IEC 60194 (1999-04)]

#### 3.1.16

#### printed circuit board

printed board that provides both point-to-point connections and printed components in a predetermined arrangement on a common base

[IEC 60194 (1999-04)]

#### 3.1.17

# rigid double-sided printed board

double-sided printed board, either printed circuit or printed wiring, using rigid base materials only [IEV 541-04-03, modified]

[IEC 60194 (1999-04)]

#### 3.1.18

#### rigid-flex printed board

a printed board with both rigid and flexible base materials

[IEC 60194 (1999-04)]

#### 3.1.19

# rigid-flex double-sided printed board

double-sided printed board, either printed circuit or printed wiring, using combinations of rigid and flexible base materials

[IEC 60194 (1999-04)]

# 3.1.20

# rigid-flex multilayer printed board

multilayer printed board, either printed circuit or printed wiring, using combinations of rigid multilayer and flexible single and double-sided base materials

#### 3.1.21

## rigid printed board

a printed board using rigid base materials only [ $IEV\ 541\text{-}04\text{-}03$ , modified] [ $IEC\ 60194\ (1999\text{-}04)$ ]

#### 3.1.22

#### rigid single-sided printed board

single-sided printed board, either printed circuit or printed wiring, using rigid base materials only [IEV 541-04-03, modified]

[IEC 60194 (1999-04)]

#### 3.1.23

# rigid multilayer printed board

multilayer printed board, either printed circuit or printed wiring, using rigid base materials only [IEV 541-04-03, modified]

[IEC 60194 (1999-04)]

#### 3.1.24

#### scratch

a narrow furrow or grove in a surface

NOTE It is usually shallow and caused by the marking or rasping of the surface with a pointed or sharp object.

[IEC 60194 (1999-04)]

#### 3.1.25

#### sequentially laminated multilayer printed board

a multilayer printed board that is formed by laminating together through hole plated double-sided or multilayer boards

NOTE Thus, some of its conductive layers are interconnected with blind or buried vias.

[IEC 60194 (1999-04)]

# 3.2 Abbreviated terms

The following abbreviated terms are defined and used within this Standard.

| Abbreviation | Meaning                         |

|--------------|---------------------------------|

| n.a.         | not applicable                  |

| NRB          | nonconformance review board     |

| PCB          | printed circuit board           |

| PID          | process identification document |

| PTH          | plated-through hole             |

| PTFE         | polytetrafluoroethylene         |

| r.m.s.       | root-mean-square                |

| TBD          | to be defined                   |

4

# **General**

This Standard details the steps to obtain from the customer the qualification for supplying PCBs of an identified technology.

These steps are:

- a. Evaluation;

- b. Qualification:

- Test and inspections,

- Qualification approval;

- c. Maintenance of qualification.

The supplier shall have or implement a quality assurance programme compatible with ECSS-Q-20.

(This page is intentionally left blank)

5

# **Evaluation**

# 5.1 General

The PCB supplier who seeks qualification of his PCB manufacturing line shall:

- a. request an evaluation;

- b. supply evaluation printed boards;

- c. submit to a manufacturing line audit.

If the result is satisfactory, the customer can authorize the go-ahead of the qualification test programme for each of the technologies that have been accepted.

# 5.2 Request for evaluation

The supplier's request for evaluation shall contain detailed description of the technology that they wish to be evaluated for. Further it shall contain a brief description of the manufacturing line, as well as details of past experience. Applications shall be signed by the person responsible for production and product assurance and shall be addressed to the customer.

# 5.3 Evaluation printed board samples

The supplier shall manufacture three PCB samples of each technology with the materials, processes and equipment that are intended for use in subsequent production for the customer. The PCBs shall represent the highest capability for which the supplier seeks approval and as far as possible conforming to this Standard.

The evaluation samples may be examined at an independent certified test house. The evaluation test performed shall be in accordance with the parameters shown as an example in annex B. The dimension of the samples shall be sufficient to contain a pattern enabling all of the listed inspections to be carried out for constructional analysis.

# 5.4 Line audit

Provided the evaluation samples are acceptable, the customer shall audit the manufacturing line when PCB production is in progress. Before or during the audit, the supplier shall make the following documents available to the customer:

- a. Company organigram related to PCB production and control, including names and functions of all key personnel involved (as defined in this Standard).

- b. Complete identification of the parameters of the technologies that they wish to qualify.

- c. List of materials and equipment (including types and names of suppliers) used for production of PCBs.

- d. List of process and control specifications with number, issue number, and date of issue or process identification document (PID).

- e. Production flow-chart, including quality-assurance inspection point and relevant process specification.

- f. Outline of test capabilities (e.g. equipment for metallographic examination, chemical analysis, failure analysis, mechanical and electrical test including functional testing of PCBs).

C

# **Qualification**

# 6.1 General

After successful evaluation and before the start of the qualification sequence the PCB supplier shall submit a qualification test programme for approval. The test programme shall conform to this clause and clause 7.

The submitted qualification test programme shall show the key personnel involved, the test houses, the proposed schedule of test and submittal of final results as required in 13.1.

The customer may witness important tests.

# 6.2 Qualification sequence

# 6.2.1 Qualification steps

- a. Qualification programme.

- b. Definition of test boards.

- c. Manufacturing of test boards.

- d. Supply of test board.

- e. Performance of test programme.

- f. Qualification test review.

- g. Qualification approval.

# 6.2.2 Qualification test programme

- a. The qualification test programme shall be performed on test boards as described in 6.3.

- b. The test boards shall be as defined in 6.4.1 and as agreed after evaluation, see clause 5.

- c. The test boards shall be supplied to ECSS-Q-70-11.

- d. Performance of test programme shall be decided according to subclauses 6.3.

- e. Qualification test review see subclause 6.5.

- f. Qualification approval, see clause 13.

No. 6

# 6.2.3 Qualification testing

Qualification testing shall be performed in the following cases:

- a. Initial qualification.

- b. When qualification took place more than two years previously and maintenance of qualification was not assured.

- c. New process technology was introduced (changes in base material, PCB structuring or chemical products requiring changes in chemical or mechanical processing parameters).

- d. The production line was moved to another location.

- e. Changes in key personnel (personnel with specialist knowledge responsible for defined production or product assurance areas).

# 6.3 Qualification test programme

# 6.3.1 Execution

The qualification test programme shall be executed in accordance with the test sequence, methods and requirements specified in Figure 1 and Table 1 on test specimens as described in subclause 6.4.

#### 6.3.2 Test sequence Test boards Reference board No. 1-6 No. 7 Group 1 Marking, visual aspect, external dimension, warp and twist Group 1.1 Group 1.2 Specific dimensional check Electrical measurements No. 1-2 No. 3-6 **Group 2 Group 3 Group 4 Group 5** Miscellaneous tests Thermal stress Thermal cycling Damp heat No. 1-2 No. 3 No. 4-5 Steam ageing

Figure 1: Qualification test flow chart

# 6.3.3 Test programme

Table 1: Test programme

|              |                                                                | Test procedure                                        |                             |

|--------------|----------------------------------------------------------------|-------------------------------------------------------|-----------------------------|

| Group        | Tests                                                          | Methods and<br>requirements<br>clause or<br>subclause | Board no. Test specimen no. |

| Group 1      | Initial test                                                   | 8                                                     | Boards 1-6                  |

| Subgroup 1.0 | Visual inspection and non-destructive tests:                   | 8.1                                                   | Boards 1-6                  |

|              | - marking                                                      | 8.1.1                                                 |                             |

|              | - visual aspect                                                | 8.1.2                                                 |                             |

|              | - external dimensions                                          | 8.1.3                                                 |                             |

|              | - warp                                                         | 8.1.4                                                 |                             |

|              | - twist                                                        | 8.1.5                                                 |                             |

| Subgroup 1.1 | Specific dimensional check                                     | 8.2                                                   | Boards 1-2                  |

| Subgroup 1.2 | Electrical measurements:                                       | 8.3                                                   | Boards 3-6                  |

|              | - intralayer <sup>0</sup> insulation resistance                | 8.3.1                                                 | Specimen A                  |

|              | - interlayer <sup>b</sup> insulation resistance                | 8.3.2                                                 | Specimen H                  |

|              | - dielectric withstanding voltage:                             | 8.3.3                                                 | 1                           |

|              | • intralayer                                                   |                                                       | Specimen A                  |

|              | • interlayer                                                   |                                                       | Specimen H                  |

|              | - continuity                                                   | 8.3.4                                                 | Specimen D                  |

|              | - interconnection resistance                                   | 8.3.5                                                 | Specimen E                  |

|              | - impedance test                                               | 8.3.6                                                 | Specimen Y                  |

|              | - dielectric constant and loss tangent for high frequency      | 8.3.7                                                 | Specimen W                  |

| Group 2      | Miscellaneous tests                                            | 9                                                     | Boards 1-2                  |

| Subgroup 2.1 | Solderability test:                                            | 9.1                                                   |                             |

|              | - wettability                                                  | 9.1                                                   | Specimen J                  |

|              | - microsectioning (option)                                     | 9.3.3                                                 | Specimen J                  |

| Subgroup 2.2 | Mechanical tests:                                              | 9.2                                                   |                             |

|              | - peel strength                                                | 9.2.1                                                 | Specimen B                  |

|              | - pull-off strength                                            | 9.2.2                                                 | Specimen B                  |

|              | - resistance to bending cycles (for flexible PCBs)             | 9.2.3                                                 | Specimen X                  |

|              | - bending test for rigid-flex                                  | 9.2.4                                                 |                             |

| Subgroup 2.3 | Coating tests:                                                 | 9.3                                                   |                             |

|              | - coating adhesion (for non-fused SnPb, Au and Au/Ni finishes) | 9.3.1.                                                | Specimen G                  |

|              | - coating analysis                                             | 9.3.2                                                 | Specimen G                  |

|              | - microsectioning                                              | 9.3.3                                                 | Specimen F                  |

$\textbf{Table 1: Test programme} \ (continued)$

|              |                                                                                                                                                                                                                                                        | Test procedure                                                                      |                                                                                                             |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Group        | Tests                                                                                                                                                                                                                                                  | Methods and<br>requirements<br>clause or<br>subclause                               | Board no. Test specimen no.                                                                                 |

| Subgroup 2.4 | Electrical tests: - current overload: • short time • long time - internal short circuit                                                                                                                                                                | 9.4<br>9.4.1<br>9.4.2                                                               | Specimen E Specimen C                                                                                       |

| Subgroup 2.5 | Physical tests: - water absorption - outgassing                                                                                                                                                                                                        | 9.5<br>9.5.1<br>9.5.2                                                               | Specimen K                                                                                                  |

| Group 3      | Thermal stress Solder bath float and vapour phase solder simulation - substrate aspect test - peel strength - continuity - interconnection resistance - microsectioning Rework simulation - microsectioning                                            | 10<br>10.2<br>8.1.2<br>9.2.1<br>8.3.4<br>8.3.5<br>9.3.3<br>10.3.<br>9.3.3           | Boards 3 Board (without specimen F) Board Specimen B Specimen D Specimen E Specimen J Specimen F Specimen F |

| Group 4      | Thermal cycling - substrate aspect test - peel strength - continuity - interconnection resistance - intralayer insulation resistance - interlayer insulation resistance - dielectric withstanding voltage: - intralayer - interlayer - microsectioning | 11<br>8.1.2<br>9.2.1<br>8.3.4<br>8.3.5<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.3<br>9.3.3 | Board 4-5 Boards Specimen B Specimen D Specimen E Specimen A Specimen H Specimen H Specimen H               |

|         |                                    | Test procedure                                        |                             |

|---------|------------------------------------|-------------------------------------------------------|-----------------------------|

| Group   | Tests                              | Methods and<br>requirements<br>clause or<br>subclause | Board no. Test specimen no. |

| Group 5 | Damp heat — Steam ageing           | 12                                                    | Board 6                     |

|         | Damp heat                          | 12.1                                                  | Board (without specimen F)  |

|         | - peel strength                    | 9.2.1                                                 | Specimen B                  |

|         | - intralayer insulation resistance | 8.3.1                                                 | Specimen A                  |

|         | - interlayer insulation resistance | 8.3.2                                                 | Specimen H                  |

|         | - dielectric withstanding voltage: |                                                       |                             |

|         | • intralayer                       | 8.3.3                                                 | Specimen A                  |

|         | • interlayer                       | 8.3.3                                                 | Specimen H                  |

|         | - microsectioning (if required)    | 9.3.3                                                 | Specimen F                  |

|         | Steam ageing                       | 12.2                                                  |                             |

|         | - Solderability test:              |                                                       |                             |

|         | • wettability                      | 9.1                                                   | Specimen F                  |

|         | - microsectioning (if required)    | 9.3.3                                                 | Specimen F                  |

**Table 1: Test programme** (continued)

# 6.4 Qualification test board

#### 6.4.1 General

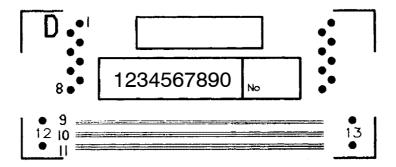

The qualification test board shall consist of a board of the highest complexity for which the supplier seeks capability approval for use in the space project. This test board shall consist of a capability specimen together with test specimens. The layout- of the test specimens shall be as described below. The layout of the capability specimen shall be agreed between customer and supplier and can be an actual PCB circuit to be used in the space project.

The test specimen design shall be in accordance with subclause 6.4.3 and the referenced IEC specification when in existence.

- Specification for single and double sided printed boards with plated-through holes (IEC 60326-5).

- Rigid multilayer printed circuit boards with interlayer connections (IEC 62326-4).

- Specification for single and double sided flexible printed boards with through connections (IEC 60326-8).

- Specification for flex-rigid multilayer printed circuit boards with through connections (IEC 60326-11).

- Sequentially laminated multilayer printed circuit boards.

- Special printed circuits boards to be defined between customer and supplier.

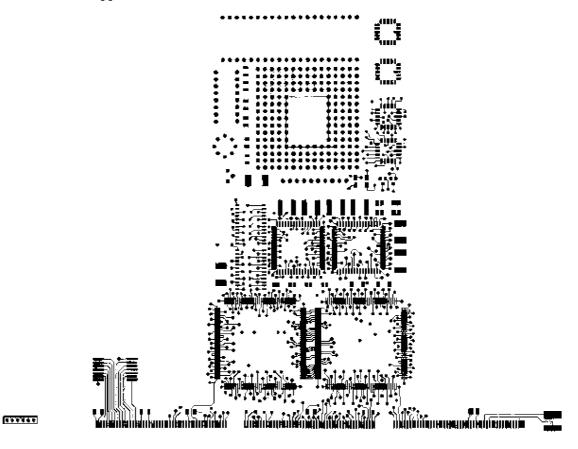

#### 6.4.2 Location of test specimens and capability specimen

An example of a qualification test board layout for a rigid multilayer board is shown in Figure 2. A similar layout may be used for other types of boards.

a i.e.: in the same layer.

b i.e.: between opposite layers

# 6.4.3 Qualification specimen design

- The individual test specimens shall represent the grade of capability of the product.

- Individual test specimens are designed to evaluate specific characteristics of the PCBs they represent.

- The normative design of test specimens shall be in accordance with the IEC specifications.

- If the supplier wishes to demonstrate the product capability by using the qualification specimen (IEC term "capability test boards"), adequate multiple arrangement for test specimens may be used (see subclause 6.4.2) as an example.

The pattern drawing on layer 1 of the individual test specimens given below and shown as an example in Figure 2 shall preferably be used.

Figure 2: Example of a qualification test board layout with test specimens and capability specimen

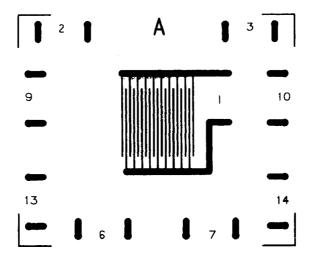

## 6.4.3.1 Test specimen A: Electrical test

- a. Intralayer insulation resistance.

- b. Dielectric withstanding voltage.

For an example of a test specimen A see Figure 3.

## Capability for all types of PCBs

- The conductor widths and spacing of each layer shall be the minimum used on the layer that is intended to be represented.

- The comb pattern can provide a useful tool for evaluating cleanliness.

Figure 3: Example of test specimen layout for intralayer insulation resistance and dielectric withstanding voltage testing

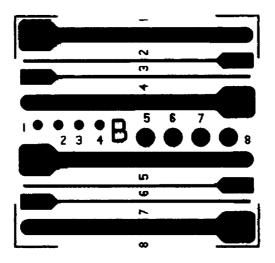

# 6.4.3.2 Test specimen B: Mechanical test

- a. Peel strength.

- b. Pull-off strength.

For an example of a test specimen B, see Figure 4.

- Conductor adhesion or plating adhesion.

- Peel strength of foil lamination.

- Pull-off strength of surface mount pads.

- Surface solderability.

NOTE This is a surface pattern only and all holes are non-plated-through.

Figure 4: Example of test specimen layout for testing peel strength of conductors and pull-off strength of pads

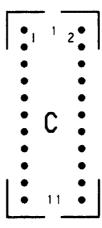

# 6.4.3.3 Test specimen C: Electrical test

Internal short circuit.

For an example of a test specimen C, see Figure 5.

# Capability for all types of PCBs

Insulation between plated-through holes in daisy chain through all layers and ground plane.

Figure 5: Example of test specimen layout for internal short circuit testing

#### 6.4.3.4 Test specimen D: Electrical test and visual aspect

- a. Etching definition.

- b. Continuity.

For an example of a test specimen D, see Figure 6.

#### Capability for all types of PCBs

- Marking.

- Etching definition.

- Continuity between plated-through holes in daisy chain through all layers.

- Visual aspect.

Figure 6: Example of test specimen layout for etching definition evaluation and continuity testing

# 6.4.3.5 Test specimen E: Electrical test

- a. Interconnection resistance.

- b. Current overload: short or long duration.

For an example of a test specimen E, see Figure 7.

#### Capability for all types of PCBs

- Interconnection resistance between plated-through holes in daisy chain through all layers before and after thermal cycling and thermal stress.

- Current overload between plated-through holes in daisy chain through all layers for short time and long time.

Figure 7: Example of test specimen layout for interconnection resistance and current overload testing

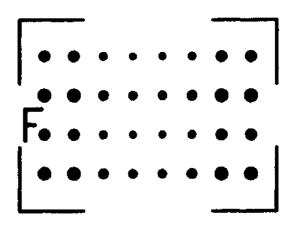

# 6.4.3.6 Test specimen F: Metal-plating test

Microsectioning.

For an example of a test specimen F, see Figure 8.

- Microsectioning to evaluate and determinate metal plating thickness.

- Microsectioning after thermal cycling, thermal stress and damp heat (optional).

Figure 8: Example of test specimen layout for microsectioning and metal plating evaluation

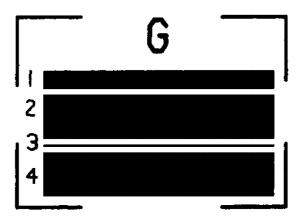

## 6.4.3.7 Test specimen G: Metal-plating/coating test

- a. Plating adhesion.

- b. Analysis of SnPb composition.

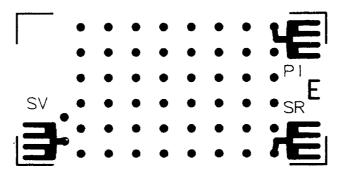

For an example of a test specimen G, see Figure 9.

#### Capability for all types of PCBs

- Plating adhesion on Cu for non-fused SnPb finishes.

- Analysis of SnPb composition after reflow.

Figure 9: Example of test specimen layout for plating adhesion testing and analysis of SnPb coating composition after reflow

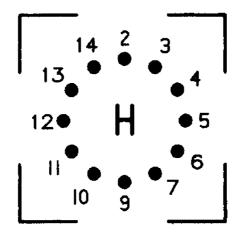

#### 6.4.3.8 Test specimen H: Electrical test

- a. Interlayer insulation resistance.

- b. Dielectric withstanding voltage.

For an example of a test specimen H, see Figure 10.

- Interlayer insulation resistance and dielectric withstanding voltage before and after thermal cycling and damp heat (optional).

- Interlayer insulation resistance and withstanding voltage measured between plated-through holes and a central ground plane.

Figure 10: Example of test specimen layout for interlayer insulation resistance and dielectric withstanding voltage testing

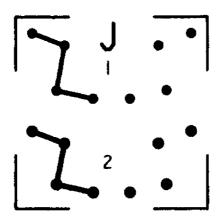

# 6.4.3.9 Test specimen J: Solderability test

- a. Solder wettability.

- b. Rework simulation.

For an example of a test specimen J, see Figure 11.

# Capability for all types of PCBs

- Wettability of solder pads and plated-through holes.

- Evaluation of plated-through hole resistance to rework or repair.

Figure 11: Example of test specimen layout for solder wettability and rework simulation testing

#### 6.4.3.10 Test specimen K: Physical test

- a. Water absorption (optional).

- b. Outgassing.

For an example of a test specimen K, see Figure 12.

- If the PCB base material is hygroscopic special care shall be taken before assembly.

- Outgassing shall be performed on base laminate material according to ECSS-Q-70-02.

Figure 12: Example of test specimen layout for water absorption and outgassing testing

#### 6.4.3.11 Test specimen L: Capability

- a. Minimum conductor width.

- b. Minimum spacing.

- c. Minimum holes diameter.

- d. Other important parameters.

For an example of a test specimen L, see Figure 13.

#### Capability for all types of PCBs

The capability specimen shall be designed to evaluate the capability of the supplier.

Figure 13: Example of test specimen layout for evaluation of capability limits

## 6.4.3.12 Test specimen M: CAD/CAM criteria

(on request only)

- a. The coupon is divided up into 3 zones with identical surfaces.

- b. Various pads in each zones (circular, oblong, square, rectangular).

- c. Thermal shunt for internal layer.

For an example of a test specimen M, see Figure 14.

#### Capability for all types of PCBs

Specimen shall be designed to evaluate the CAD/CAM capability of the supplier.

Figure 14: Example of test specimen layout for evaluation of CAD/CAM capability

#### 6.4.3.13 Test specimen X: Resistance to bending cycles

Resistance to bending.

For an example of a test specimen X, see Figure 15.

#### Capability for all types of PCBs

- Evaluation of continuity of conductors in flexible part.

- Evaluation of adhesion of conductors and insulating material.

Figure 15: Example of test specimen layout for testing resistance to bending cycles

# 6.4.3.14 Test specimen Y: Electrical test (on request)

Impedance.

For an example of a test specimen Y, see Figure 16.

#### Capability for all types of PCBs

Evaluation of controlled impedance capability.

Figure 16: Example of test specimen layout for controlled impedance testing

# 6.4.3.15 Test specimen W: Electrical test for high frequency circuits (on request)

- a. Dielectric constant.

- b. Loss tangent.

#### Capability for all types of PCBs

Resonator for dielectric constant and loss tangent measurements (to be defined between supplier and customer). The resonator will depend on the dielectric parameters of the material.

#### 6.5 Qualification programme

#### **6.5.1** General

- The qualification programme of PCBs for space applications shall be performed on the six PCB qualification test boards.

- One additional PCB qualification test board shall be made for reference.

- The qualification test boards shall be manufactured according to ECSS-Q-70-11.

- The qualification programme shall be performed by the customer, one or more independent test houses or the PCB supplier. Each test house shall have customer approval prior to commencement of the programme. The programme shall be monitored by the customer at various stages during testing. A comprehensive test report shall be established for review together with all microsections.

- In the case of a qualification extension due to changes in technology the extension qualification programme and qualification test boards shall be negotiated between the customer and supplier.

- If the PCBs are used for manned space programmes the customer shall assure the PCB base material is tested for flammability according to ECSS-Q-70-21 as well as offgassing (toxicity) and odour according to ECSS-Q-70-29. This is the responsibility of the customer.

#### 6.5.2 Nonconformance criteria

- PCB process nonconformances shall be subjected to the dispositions as defined according to quality assurance requirements in ECSS-Q-20-09.

- The nonconformance criteria for a specific test is detailed in the relevant test clause and the minimum requirement for the specific type of PCB is detailed in the relevant table in clause 17.

- Major and minor nonconformances.

- 1. Any major nonconformance (M) can result in the failure of qualification. This is dispositioned at a nonconformance review board (NRB) established by the customer and the PCB supplier.

- 2. Minor nonconformances (**m**) shall be reported and submitted with the qualification report and are considered in the customer's judgement of qualification approval. The supplier shall initiate an internal NRB to determine the causes and consequences.

- 3. If a criterion is marked m/M, the supplier shall agree with the customer what is to be regarded as a minor or a major nonconformance.

7

# Test and inspections

#### 7.1 Test condition

Unless otherwise specified, all tests shall be carried out under normal atmospheric conditions (specification IEC 60326-2 am 1 (1992-06) test 18 a).

• Room temperature:  $(22 \pm 3)$  °C • Relative humidity:  $(55 \pm 10)$  %

• Atmospheric pressure

Before testing is started, the PCBs shall be subjected for 48 h to ambient conditions.

During a sequence of measurements, the atmospheric conditions in the test area shall not undergo significant or rapid changes. These conditions shall be noted in the test reports. In case of dispute, the measurements shall be taken under reference atmospheric conditions.

The PCBs to be tested shall not be covered with a protective varnish.

During the testing period, the following precautions shall be taken:

- Keep the boards flat against a plane surface.

- Boards used for electrical tests shall be protected from any contamination and shall be held by their edges during the tests.

- Before environmental exposure, soldering operation, electrical and mechanical testing, the boards shall be cleaned according to ECSS-Q-70-08.

#### 7.2 Test descriptions

The following clauses give the description of the tests for the PCB specimens according to Figure 1 and Table 1. The accept/reject criteria are given with indication of major  $(\mathbf{M})$  or minor  $(\mathbf{m})$  nonconformances (see 6.5.2).

(This page is intentionally left blank)

# Group 1 — Initial test

#### 8.1 Subgroup 1.0 - Visual inspection and non-destructive test

#### 8.1.1 Verification of marking

#### a. Procedure

Each board shall be inspected with the naked eye for correct marking. The marking shall be legible and resistant to test stresses.

#### b. Nonconformance criteria

| Identification impossible                        | M |

|--------------------------------------------------|---|

| Marking not conforming to customer specification | M |

| Defects not affecting identifications            | m |

#### 8.1.2 Visual aspects

#### a. Procedure

Each board shall be inspected by magnification  $\leq \times 10$  with suitable lighting conditions to verify that construction and workmanship meet the requirements. In case of any irregularity, the area shall be examined under  $\times 20$  –  $\times 40$  magnification.

#### b. Nonconformance criteria

#### 1. General cleanliness and contamination

| Contamination visible to the naked eye and not removable by cleaning according to ECSS-Q-70-08 | M |

|------------------------------------------------------------------------------------------------|---|

| Contamination visible to the naked eye but removable by cleaning according to ECSS-Q-70-08     | m |

#### 2. Substrate

| Not in conformity with suppliers trademark and required quality                        | M |

|----------------------------------------------------------------------------------------|---|

| Scratches cutting glass fibre or leaving marks in the dielectric affecting reliability | M |

| Scratches not affecting reliability                                                    | m |

| Dents, crazing and haloing                                                      |     |

|---------------------------------------------------------------------------------|-----|

| - visible to the naked eye                                                      | M   |

| - not visible to the naked eye                                                  | m   |

| Non-homogeneity regarding colouring and opacity                                 | m/M |

| Discoloured copper oxide layer on internal layer is acceptable                  |     |

| Inclusion of foreign matter, blistering or air bubbles                          |     |

| - visible to the naked eye                                                      | M   |

| - not visible to the naked eye                                                  | m   |

| Delamination                                                                    | M   |

| Measling                                                                        |     |

| - generalized                                                                   | M   |

| - localized reducing insulation distance in the outer layer out of tolerance    | M   |

| - localized not reducing insulation distance in the same layer out of tolerance | m   |

| Fungus growth                                                                   | M   |

| Delamination of cover lay (flexible PCB)                                        | m/M |

#### 3. Non-plated-through holes

| Holes plated unintentionally                            | m/M |

|---------------------------------------------------------|-----|

| Incompletely drilled holes, missing or additional holes | m/M |

#### 4. Routing

| Incomplete routing of board, so that dimensional or mechanical requirements are not met | M |

|-----------------------------------------------------------------------------------------|---|

| Random cutting defects acceptable within the dimensional requirements                   | m |

#### 5. Surface metallization

| Conductors or pads not conforming to customer's layout                                                     | M   |

|------------------------------------------------------------------------------------------------------------|-----|

| Terminal pads or conductors completely or partially missing, cut, forming a short circuit                  | M   |

| Lifting of conductive pattern from substrate                                                               | M   |

| Scratches exposing copper plating                                                                          | M   |

| Copper or nickel visible on top surface plated areas                                                       | M   |

| Large number of superficial scratches not attributed to a manufacturing process evidencing bad workmanship | M   |

| Dewetting of solder pads on fused tin lead finish                                                          | M   |

| Granular aspect of solder pads on fused tin lead finish                                                    | m/M |

| Corrosion of copper                                                                                        | M   |

| Migration of copper through gold                                                                           | M   |

#### 6. Plated-through holes

| Incompletely drilled, additional or missing holes                                                           | M   |

|-------------------------------------------------------------------------------------------------------------|-----|

| Missing metallization                                                                                       | M   |

| Component holes $\geq 0.6$ mm filled or partially filled with solder resulting in out of tolerance diameter | m/M |

#### 7. Random defects of conductors and terminal pads

Intermittent and irregular defects which affect metallization, e.g. edge roughness (peak or valley), pits, pin holes, voids, protrusions or indentations.

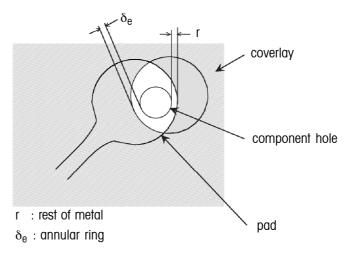

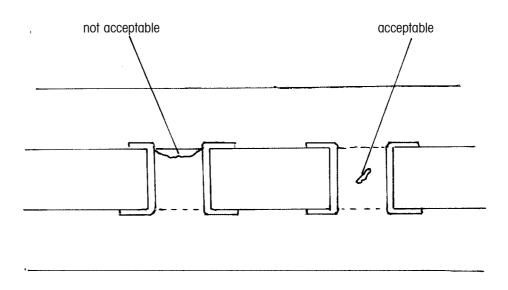

Protrusion or indentations of metallization on conductor edge or voids in conductor as shown in Figures 17, 18 and 19.

x: nominal conductor width

Figure 17: Random defects of conductors and terminal pads

| $a \leq 20~\%$ of x and conductor width > minimum requirement | m |

|---------------------------------------------------------------|---|

| a > 20 % of x or conductor width < minimum requirement        | M |

| $b \le x$                                                     | m |

| b > x                                                         | M |

y: nominal spacing between conductors

Figure 18: Random defects between two conductors

| Opposite peaks: if $z < 80 \%$ of y                                                             | M |

|-------------------------------------------------------------------------------------------------|---|

| Isolated peaks or valleys: $h > 20 \%$ of x and z < minimum requirement                         | M |

| Conducting island: a + h > 20 $\%$ of y and the isolation spacing < minimum spacing requirement | M |

| a > 20 % of y or y - a < minimum requirement                                                    | M |

| b > y                                                                                           | M |

| Cover lay (flexible PCBs) covering part of solder pad                                           | M |

Figure 19: Misalignment of coverlay

#### 8.1.3 External dimensions

#### a. Procedure

Each board shall be measured by means of suitable standard measuring equipment to verify that the physical dimensions, including board thickness and external dimensions meet the customer's specifications.

#### b. Nonconformance criteria

1. Thickness of base laminate (average of 4 measurements on the board)

| f out of tolerance M |

|----------------------|

|----------------------|

2. Length and width of board (average of 2 measurements on the board)

| If out of tolerance | M |

|---------------------|---|

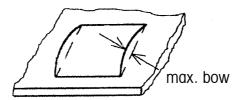

#### 8.1.4 Warp

#### a. Procedure

The PCBs shall be placed unrestrained on a plane horizontal surface with the convex side upward. The warp shall be expressed in percentage terms.

- Measure maximum bow between the plane horizontal surface and the PCB as defined in Figure 20.

- Measure the length of the PCB.

- Calculate the warp percentage:

$$Warp ~\% = \frac{Max.~blow~in~mm}{Length~of~the~PCB~in~mm} \times 100$$

Figure 20: Warp

#### b. Nonconformance criteria

| If more than maximum bow | M |

|--------------------------|---|

|--------------------------|---|

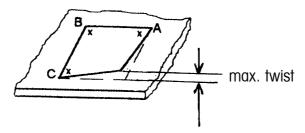

#### 8.1.5 Twist

#### a. Procedure

The PCB shall be placed on a plane horizontal surface so that it rests on three corners. The height of the remaining corner from the surface shall then be measured (expressed in percentage terms).

- Measure the distance between the plane horizontal surface and the fourth corner of the PCB, as defined in Figure 21.

- Measure the length of the diagonal.

- Calculate the twist percentage:

$$Twist ~\% = \frac{Max.~twist~in~mm}{Length~of~the~diagonal~in~mm} \times 100$$

A, B and C are touching base

Figure 21: Twist

#### b. Nonconformance criteria

| If more than maximum twist | M |

|----------------------------|---|

|----------------------------|---|

### 8.2 Subgroup 1.1 — Specific dimensional check

- a. The points to be measured on test coupons and circuit shall be decided between suppliers and customers and shall include for example:

- minimum and maximum plated-through holes diameter and soldering pads diameter;

- minimum and maximum conductor width;

- minimum and maximum distance between conductors.

- b. The measurements shall be presented in tabular form for better readability.

| Plated-through holes |         |          |           |          |           |

|----------------------|---------|----------|-----------|----------|-----------|

| Measuring            | Test or | Øı       | pad       | Øŀ       | nole      |

| point                | coupon  | Measured | Deviation | Measured | Deviation |

|                      |         |          |           |          |           |

|                      |         |          |           |          |           |

|                      |         |          |           |          |           |

| Conductor's widths |                |                       |           |

|--------------------|----------------|-----------------------|-----------|

| Measuring point    | Test or coupon | Measured<br>dimension | Deviation |

|                    |                |                       |           |

|                    |                |                       |           |

|                    |                |                       |           |

| Spacing between conductors |                |                       |           |

|----------------------------|----------------|-----------------------|-----------|

| Measuring point            | Test or coupon | Measured<br>dimension | Deviation |

|                            |                |                       |           |

|                            |                |                       |           |

|                            |                |                       |           |

#### c. Procedure

Measurements of dimensional parameters relating to metal plating (e.g. width of conductors, spacing, minimum annular ring metal) shall be taken at the copper/board base interface or for high frequency circuits as required by the customer (see subclause 9.3 Figure 23). Hole diameters may be measured with measuring gauges or a measuring microscope.

#### d. Nonconformance criteria

| All dimensions (e.g. diameter of holes, width of conductors and | M |

|-----------------------------------------------------------------|---|

| diameter of terminal pads) which do not conform to the circuit  |   |

| definition document and acceptable tolerance limits             |   |

| For non-soldering holes: diameter out of tolerance              | m |

#### 8.3 Subgroup 1.2 — Electrical measurements

#### 8.3.1 Intralayer insulation resistance on specimen A

According to tests 6a and 6b of IEC 60326-2 am 1 (1992-06).

#### a. Procedure

A direct voltage of  $(500 \pm 50)$  V shall be applied between the two closest conductors which are not electrically connected. The insulation resistance (R) is measured 1 min after the voltage has been applied.

b. Nonconformance criteria

| If R is less than minimum requirement | M |

|---------------------------------------|---|

|---------------------------------------|---|

#### 8.3.2 Interlayer insulation resistance on specimen H

According to tests 6c of IEC 60326-2 am 1 (1992-06).

#### a. Procedure

Carry out the test as before, the voltage being applied between two ground planes (or between one ground plane and one conductor) that are superimposed.

b. Nonconformance criteria

| If R is less than minimum requirement | M |

|---------------------------------------|---|

|---------------------------------------|---|

# 8.3.3 Dielectric withstanding voltage intralayer on specimen A and interlayer on specimen H

According to tests 7a and 7b of IEC 60326-2 am 1 (1992-06).

#### a. Procedure

The test voltage shall be applied between two superimposed conductors (i.e. between layers), or between two adjoining (but not electrically connected) conductors within the same layer. The AC voltage at 50 Hz is gradually applied progressing from 200 V r.m.s. per second up to 1500 V r.m.s. per mm of spacing between two conductors. This voltage shall be kept steady for one minute, with the current limited to 100  $\mu A.$

Final measurements: aspect and continuity.

b. Nonconformance criteria

| Evidence of breakdown, flashover or sparking | M |

|----------------------------------------------|---|

|----------------------------------------------|---|

#### 8.3.4 Continuity on specimen D

According to test 3a of IEC 60326-2 am 1 (1992-06).

Conductor continuity is tested by measuring the interconnection resistance on specimen D.

#### a. Procedure

The measurement shall be taken using a method ensuring an error no greater than 5% (four wires method).

The current shall be limited to  $0,1~\mathrm{A}.$

The measuring voltage shall not exceed 5 V.

The post-test measurements taken on each sample shall be compared with pre-test measurements.

#### b. Nonconformance criteria

| Discontinuity                                          | M   |

|--------------------------------------------------------|-----|

| Dispersion greater than $\pm 10$ % with respect to the | m/M |

| mean of values measured on the specimens               |     |

#### 8.3.5 Interconnection resistance on specimen E

According to test 3b of IEC 60326-2 am 1 (1992-06).

a. Procedure

Same test conditions as for continuity testing.

b. Nonconformance criteria

| Discontinuity                                                  | M |

|----------------------------------------------------------------|---|

| Dispersion greater than $\pm 10$ % with respect to the mean of |   |

| values measured on the specimen                                | M |

#### 8.3.6 Impedance test on specimen Y

According to test 9a of IEC 60326-2 am 1 (1992-06).

The measuring method shall be specified by the customer.

# 8.3.7 Dielectric constant and loss tangent for high frequency materials on specimen W

The measuring method shall be specified by the customer.

- Annular ring.

- Closed cavity or other method.

9

# Group 2 — Miscellaneous tests

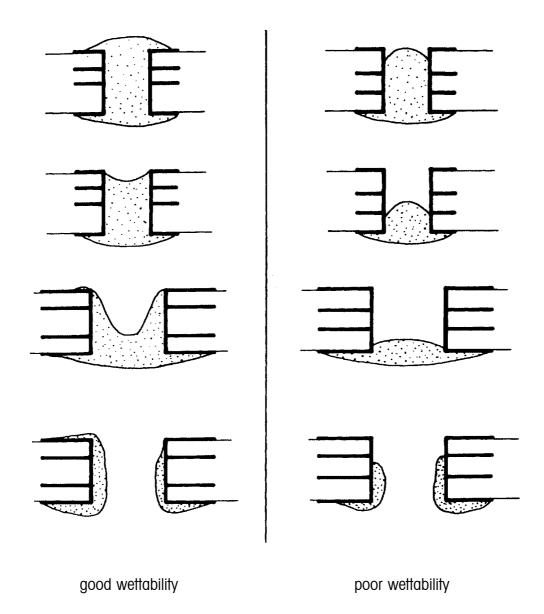

#### 9.1 Subgroup 2.1 — Solderability test — Wettability on specimen J

According to test 14a of IEC 60326-2 am 1 (1992-06) and IEC 60068-2-20 am 2 (1987-01), test TC.

- a. Procedure

- Non-activated rosin-based flux as specified in ECSS-Q-70-08.

- Solder

Tin lead 60/40 or 63/37 as specified in ECSS-Q-70-08.

- Test machine Rotary dip tester or similar equipment.

The specimens are fluxed by immersion.

Surplus flux is removed by keeping the specimens upright for 5 min.

The specimen is arranged on the soldering machine and brought into contact with the surface of the solder bath that is kept at the temperature of  $(235\pm5)$  °C during:

- 3 s (wetting time),

- 10 s (dewetting time).

- b. Inspection

A visual inspection is made with a  $\times 10$  magnification.

A microsection can also be performed and a visual inspection made at a magnification greater than  $\times 100$ .

c. Nonconformance criteria

| Poor wettability of solder pads and plated-through holes: see Figure 22 | M |

|-------------------------------------------------------------------------|---|

| Microsectioning                                                         |   |

| Broken metallization                                                    | M |

Figure 22: Wettability of terminal pads and plated-through holes

## Subgroup 2.2 — Mechanical tests

#### 9.2.1 Peel strength on specimen B

According to test 10a of IEC 60326-2 am 2 (1992-06).

#### a. Procedure

The conductor selected is peeled back at one end for a length of about 10 mm.

The detached end of the conductor is firmly gripped over its whole width and traction is then applied in a direction perpendicular to the plane of the PCB until the copper starts to peel away.

The rate of traction is kept constant at 50 mm/min. The traction direction is kept perpendicular to the plane of the PCB. Machine inertia shall have no effect on the measurement. The conductor width to be taken into account shall be the actual width where the conductor is stuck to the insulation.

9.2

#### b. Nonconformance criteria

Peel strength

| If less than minimum requirement | M |

|----------------------------------|---|

|----------------------------------|---|

#### 9.2.2 Pull-off strength on specimen B

According to test 11a of IEC 60326-2 am 1 (1992-06).

- a. Procedure

- Temperature of iron:  $(270 \pm 10)$  °C.

- Solder: Tin-lead 60/40 or 63/37 alloy with non-corrosive resin core as specified in ECSS-Q-70-08.

After application of the soldering flux specified in IEC 60068-2-20 am 2 (1987-01), test TC, the pads shall be tinned for  $(4 \pm 1)$  sec.

A tinned copper wire with a diameter 0,3 mm less than the hole diameter and of 150 mm approx. lengths shall be used.

Soldering shall be between 2 s and 3 s.

After another 5 min ambient reconditioning the soldering operations shall be repeated (second soldering).

• Ambient reconditioning:

The ambient reconditioning time before final measurement shall be more than 10 min.

Final measurement:

Force is applied using a traction machine pulling on the wire. This force increases with a constant rate of between 5~N/s and 50~N/s until the terminal pad separates from the board base material (chosen value 10~N/s).

b. Nonconformance criteria

Pull-out strength for terminal pads.

| If less than minimum requirement | M |

|----------------------------------|---|

|----------------------------------|---|

# 9.2.3 Flexural fatigue on specimen X (for double sided flexible PCB)

According to test 21a of IEC 60326-2-am 1 (1992-06).

a. Procedure

Equipment similar to that described in IEC 60249-1-am 4 (1993-05) subclause 3.12-2 and Figure 13.

Short insulated wires are connected to the ends of the conductive patterns (front and backsides in series). The test specimen is mounted on the device such that the interior diameter of the loop is  $(9.6 \pm 0.4)$  mm.

The alternating movement shall be such that the loop moves at least 25 mm and that the test specimen is not curved at either end.

The pace of the alternating movement shall not exceed ten cycles per minute.

The test consists of maintaining the alternative movement until an electrical discontinuity appears or until the 500 cycles required is completed without a defect.

#### b. Nonconformance criteria

| Discontinuity appearing before 250 cycles                 | M   |

|-----------------------------------------------------------|-----|

| Discontinuity appearing between 250 cycles and 500 cycles | m   |